# BLOCK II: MEMORY AND I/O MANAGEMENT, SYSTEM DEADLOCK AND MULTIPROGRAMMING SYSTEM

- Unit 1 : Memory Management

- Unit 2 : Input-Output Organization

- Unit 3 : Introduction to Deadlock

- Unit 4 : Deadlock Prevention, Detection and Avoidance

- Unit 5 : Multiprogramming System

- Unit 6 : Secondary Storage Management

- Unit 7 : Security

- Unit 8 : Distributed Operating System

# **UNIT 1: MEMORY MANAGEMENT**

#### Unit Structure:

- 1.1 Introduction

- 1.2 Unit Objectives

- 1.3 Hierarchy of Memory Types

- 1.4 Cache Memory

- 1.5 Associative Memory

- 1.6 Address Protection

- 1.7 Paging1.7.1 Paging Hardware Support1.8 Segmentation

- 1.8.1 Segmentation Hardware

- 1.9 Virtual memory 1.9.1 Demand Paging

- 1.10 Page Replacement Algorithms

- 1.10.1 FIFO Page Replacement

- 1.10.2 LRU Page Replacement

- 1.10.3 Optimal Page Replacement

- 1.11 Summing Up

- 1.12 Answers to Check Your Progress

- 1.13 Possible Questions

- 1.14 References & Suggested Readings

# **1.1 INTRODUCTION**

The unit deals with management of main memory during process execution. One of the most important functions of operating system is memory management that includes the hardware support in processor for paging, virtual memory and segmentation. Virtual memory allows a program with memory space larger than the size of the main memory available in the system. This is possible by allowing only that section of the code that is active at that point of time without the need of having all instructions and data of the process being present in main memory at the same time. The concept of paging and segmentation eliminates the need of allocating main memory to the process in contiguous manner. Also if the overall memory requirement exceeds the physical memory limit,

pages from memory may need to be replaced to make room for new pages. Various page replacement algorithms like FIFO, LRU and Optimal are used in such case.

## **1.2 UNIT OBJECTIVES**

After going through this unit, you will be able to:

- explain memory hierarchy, cache memory and associative memory

- explain the working of memory address protection.

- explain the paging memory management scheme.

- analyze and solve problems on paging.

- explain the working of paging hardware.

- explain the concept of segmentation and solve problems on segmentation.

- describe the benefits of Virtual memory management system

- explain and solve problems on different page replacement algorithms.

## **1.3 HIERARCHY OF MEMORY TYPES**

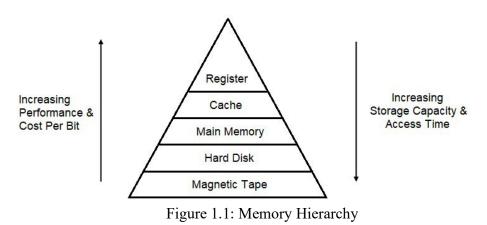

The memory in a computer system can be divided into a hierarchy as shown in Figure 1.1. The hierarchy is based on access time, speed, cost and capacity of the memory. The five memory types in the hierarchy are registers at the top followed by the cache memory, main memory, hard disk and magnetic tapes. The first three memory types register, cache and main memory are volatile memories that is they lose their stored data in absence of power supply. The last two memory types, hard disk and magnetic tape keeps the stored data permanently even in the absence of power.

In the Figure 1.1, capacity that is the volume of information the memory can store increases as we move from top to bottom in the hierarchy.

Access time that is time required to perform read/write request increases as we move from top to bottom in the hierarchy. Similarly, the speed gap between CPU and memory decreases as we move from bottom to top of the hierarchy and finally cost per bit increases going from bottom to top of the hierarchy.

Space for learners:

## **1.4 CACHE MEMORY**

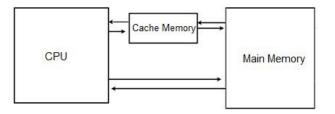

Cache Memory is a type of memory that operates at a very high speed. It's used to boost performance and synchronize with a high-speed CPU. Although cache memory is more expensive than main memory but it is less expensive than CPU registers. Cache memory acts as a buffer between the main memory and the CPU as shown in Figure 1.2. Cache memory stores frequently requested instructions and data so that they may be accessed quickly by the CPU. It smaller and faster memory that reduces the average access time of main memory by storing copies of most frequently used data.

# Figure 1.2: Cache Memory acting as a buffer between CPU and Main Memory.

## **1.5 ASSOCIATIVE MEMORY**

Associative memory is also known as Translation Lookaside Buffer (TLB) is a special type of memory that is optimized to perform parallel searches on data, in contrast to sequential search of data.

Operating system provides support for storing page table of a process. Generally, a page table can be stored in following ways:

- Set of dedicated registers

- In main memory

- Associative Memory or Translation lookaside buffer (TLB)

The feasibility of the first approach using a set of dedicated registers is that the page table should be reasonably smaller in size like 256 entries. With the second approach page table can be very large like millions of entries can be stored in the main memory with a pointer to the starting address of the page table for referencing. However, in this case the time required to access the page table is slower by a factor of two as it involves first accessing memory for the page table to locate the frame number which is combined with the displacement to get the physical address and then a second memory access to read the byte.

The solution to the disadvantages of the first two approaches is resolved using a fast lookup hardware support called Associative memory. Associative memory or TLB is a small, expensive but very fast associative memory. It can store entries in the range of 64 to 1024. Associative memory has two parts: a tag and a value. When a page/key needs to be searched the key is compared simultaneously with all the tags of the in the associative memory.

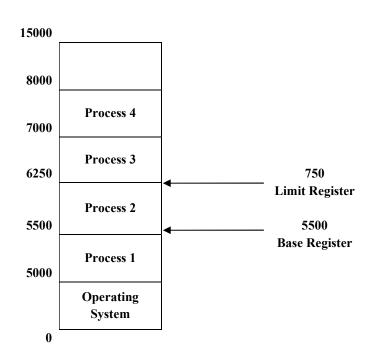

#### **1.6 ADDRESS PROTECTION**

In a main memory there can be several user process and operating system running at a time. To protect the address space of the operating systems as well as user processes, so that they do not run into to each other's address space, the concept of hardware address protection is introduced. Address protection is implemented with the help of two registers, the *base register* and the *limit register*. The base register holds

the starting address of the process address and the limit register specifies the range. For example, in Figure 1.3, the base register holds the starting address 5500 of *Process-2* in the main memory and the limit register specifies range of 750 meaning that the range of legal address of *Process-2* is from 5500 to 6249 (inclusive).

Figure 1.3: A logical address defined by base and limit register.

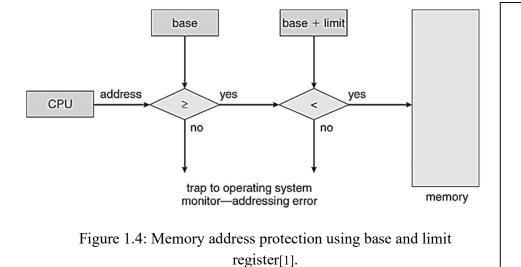

The Memory address protection is accomplished with the help of hardware support as shown in Figure 1.4. The hardware checks that the CPU generated address is within the range specified by *base register* and *base* + *limit register*. A memory access attempted outside the valid range, results in trap or a fatal error.

Space for learners:

## 1.7 PAGING

To understand the concept of Paging we have to go through the following concepts:

- Process: It is a program in execution or a program placed in main memory for execution.

- Logical Address: It is the address that is generated by the CPU for a program while it is running. As the address does not exist physically it is also called virtual address. The hardware unit of memory known as memory management unit (MMU) maps logical address to physical address.

- Physical Address: A physical address is the actual address in the main memory.

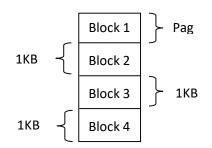

Paging is a memory management scheme that is used to map CPU generated logical address of a process to physical address in main memory. A process consists of fixed size blocks; Figure 1.5 shows an example of a process with 4 blocks each of size 1 kilobyte. Size of a block depend upon architecture of the computer and varies between 512 bytes to 16 megabytes.

Figure 1.5: A Process with 4 blocks each of size 1 kilobyte.

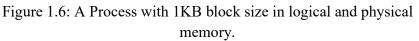

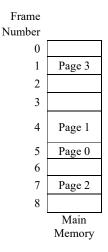

The paging technique divides the logical memory to blocks of the fixed size known as Pages and divides physical memory into blocks of fixed-size known as Frames. Figure 1.6 shows an example of pages and frames in logical and physical memory respectively.

|   | Page 1  | 1KB | Frame 1  | 1KB |

|---|---------|-----|----------|-----|

|   | Page 2  | 1KB | Frame 2  | 1KB |

|   | Page 3  | 1KB | Frame 3  | 1KB |

|   | Page 4  | 1KB | Frame 4  | 1KB |

| - | Logical |     | Physical |     |

|   | Memory  |     | Memory   |     |

Page 0Page 1Page 2Page 3Logical

memory

Figure 1.7: Paging model of physical and logical memory.

Paging scheme allows a process to be stored in the main memory in noncontiguous manner. It also solves the problem of searching and fitting blocks of different sizes in main memory by having all block of same size. One more advantage of the paging scheme is that it prevents from external fragmentation that is if the main memory blocks are of varying sizes and the size of the free blocks are smaller than the size of the pages, then the operating will be required to merge two or more blocks into a single block large enough to fit a page. By keeping block of equal sizes for both pages and frames, such problems are resolved. The Figure 1.7 shows paging model of physical and logical memory. A page table is used for mapping between logical addresses and physical addresses. A page table resides in the main memory. The Figure 1.7 shows noncontiguous allocation of a process in main memory. The mapping of logical address to physical address is achieved using the page table.

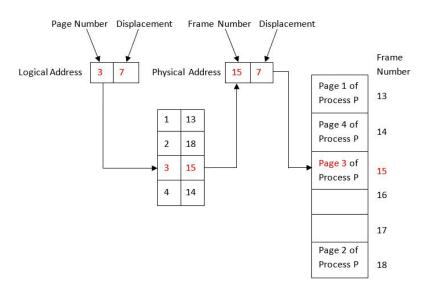

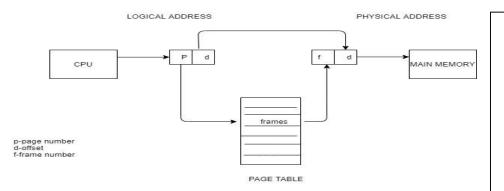

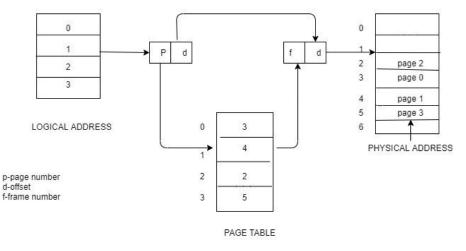

The hardware support for paging is demonstrated using an example in Figure 1.8. The logical address generated by the CPU is divided into two parts namely *page number* and *displacement* with the page. The page number is used as an index in the page table to search for the corresponding frame number. The displacement is combined with frame number to get the physical address. In the Figure 1.8, the logical address having *page number 3* is searched for the corresponding frame number in the page table which is *frame number 15*. The *frame number 15* is combined with the *displacement 7* to form the physical address.

#### Space for learners:

Figure 1.8: Paging hardware support.

If the size of the logical address space is  $2^m$  and size of a page is  $2^n$  bytes/words, then "*m*-*n*" bits of a logical address designate the page number the "*n*" bits designate the displacement or offset. Therefor the logical address is:

| Page Number | Displacement |

|-------------|--------------|

| р           | d            |

| m - n       | n            |

#### **Paging Example -1:**

Assume a page size of 1K and a 15-bit logical address space. How many pages are in the system?

#### Solution:

Page size =  $1K = 2^{10}$  i.e. displacement, n=10 bits No. of bits in logical address = 15, i.e. m=15 bits. Therefore, no. of bits used for page number is, m - n = 5 bits Total no. of pages in the system is  $2^5 = 32$ .

#### **Paging Example -2:**

Assume that a CPU has a 15-bit logical address space with 8 logical pages. How large are the pages? **Solution:**

There are 8 logical pages, that means 3 bits are required to address 8 logical pages  $(2^3 = 8)$ . Therefore, m - n=3 bits Logical address is 15 bits, m=15 bits Displacement = 15 -3 = 12 bits. So, the pages are of size  $2^{12} = 4096 = 4$ K bytes

## **1.7.1 Paging Hardware Support**

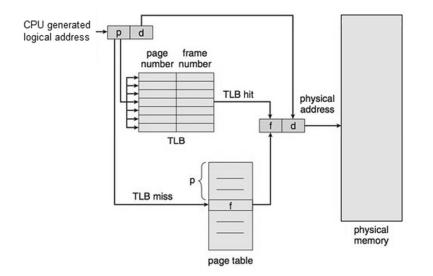

The operating system provides hardware support for quick search in the form of Associative memory or TLB. There are possibly two cases for a page search in TLB, Figure 1.9 illustrates the paging hardware with Translation Look aside Buffer for these two cases:

- If the search key/page is found it is called as a*TLB hit* and corresponding value/frame is returned from the TLB. Displacement is combined with frame number and the physical address is accessed.

- If the search key/page is not found it is called as a*TLB miss* and the page is searched in the page table stored in main memory. The frame number corresponding to the search page is combined with the displacement to access the address in the physical memory. Also the page number and frame number is added to the TLB so that if the same page is referred next time it is found quickly. In case the TLB is full, operating system selects a page replacement algorithm to replace an existing page with the new entry.

The percentage of times that a particular page number is found in the TLB is called the *hit ratio*. If the hit ratio is 60% that means 60 times out of 100 references the page will be found in TLB and remaining 40 times the page is found in the page table.

Space for learners:

Figure 1.9: Paging hardware with Translation Look aside Buffer [1].

#### Paging Example -3:

If it takes 25 nanoseconds to search the TLB and 75 nanoseconds to access memory. If the hit ratio is 70%, calculate effective memory access time.

#### Solution:

If the page is in the TLB, time taken to access the physical address

= Time taken to search the TLB + Time taken to access memory

= 25 + 75 = 100 nanoseconds

If the page is in not in the TLB, time taken the physical address

= Time taken to search the TLB + Time taken to access page table + Time taken to access memory

= 25 + 75 + 75

= 175 nanoseconds

Hit ratio is 70%, therefore Effective access time = 0.70 X 100 + 0.30 X 175 =122.5 nanoseconds.

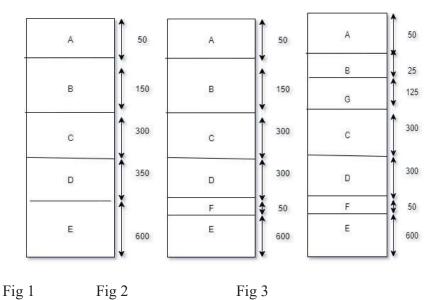

## **1.8 SEGMENTATION**

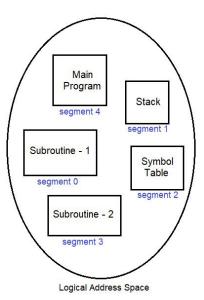

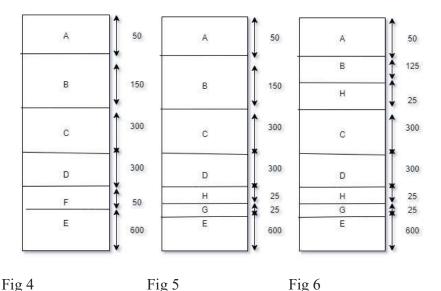

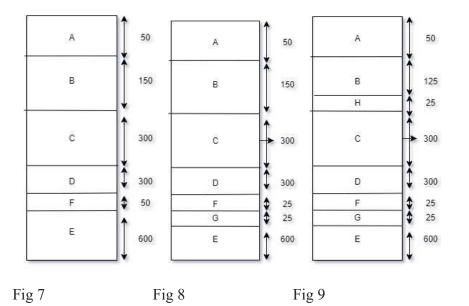

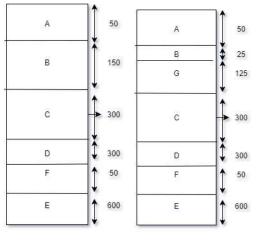

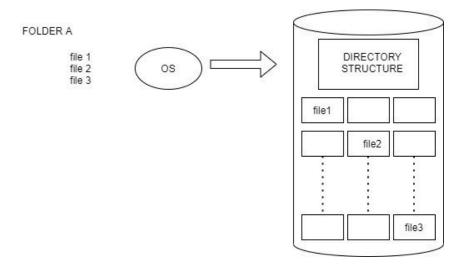

Segmentation is a memory management scheme similar to paging that allows a process to be stored in the main memory in noncontiguous manner. Unlike paging where all the pages or frames are of fixed size, segmentation allows blocks or segments of variable size. Segmentation maps the user's view of a program onto the physical memory. Looking at the user's view in Figure 1.10, a program contains several variable size segments, such as the main program, subroutine, symbol table, methods etc. It also includes data structures like arrays, objects, variables, stacks etc. These segments and data structures are referred by their name without concerning about the address these segments are stored in memory. Users are not concerned about the order in which the segments are stored in the memory.

Figure 1.10: User's view of a program

The logical address space is a group of segments. Each segment has a name and a length. From the implementation point of view, segments are numbered instead of using name and the logical address is represented using the *two tuple*:

| Segment-number Disp |

|---------------------|

|---------------------|

#### **1.8.1 Segmentation Hardware**

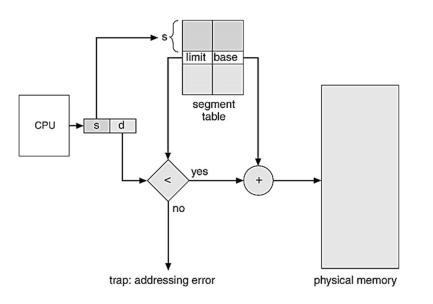

The mapping of the logical address <segment-number, displacement> to the physical address is achieved with the help of segment table and the segmentation hardware as shown in Figure 1.11. Each entry of the segment table has a segment limit and segment base. The base represents the starting address of the segment in the main memory and the limit specifies the length of the segment. The segment table is indexed on the segment number.

Figure 1.11: Segmentation Hardware[1].

The working of segmentation hardware starts by first identifying the segment number, *s* and the displacement, *d*of the logical address. The segment number is used to search the segment table, which is indexed on the segment number. The displacement, *d*of the logical address should be between 0 and limit. If the condition is not satisfied, it means that the logical address is going beyond the segment limit and a trap interrupt is initiated which is handled by the operating system.

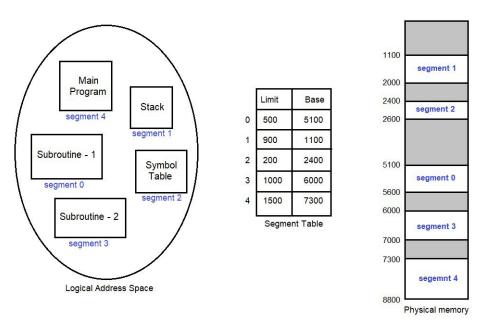

A segmentation example is shown in Figure 1.12. There are 5 segments numbered from 0 through 4. The segments are stored in physical memory in noncontiguous manner. Also no specific ordering is followed for storing the segments as can be observed in the example. The segment table has an entry for each of the segment, the starting

address of the segment mentioned as *base* and the length of the segment mentioned as *limit*. For example, segment 0 begins at address 5100 and length of the segment is limited to 500 bytes. Therefore, a reference to byte 17 of segment 0 is mapped to 5100 (base of segment 0) + 17 = 5117. Similarly, a reference to byte 88 of segment 4 is mapped to 7300 + 88 = 7388. A trap interrupt will be called if byte 1700 of segment 4 is referenced as the limit is 1500.

Figure 1.12: Example of Segmentation.

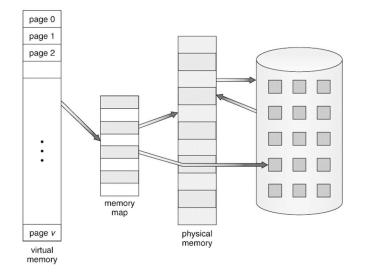

## **1.9 VIRTUAL MEMORY**

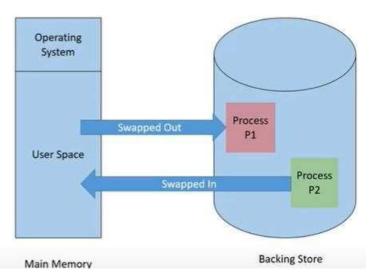

The memory management scheme discussed in previous section requires the entire process to be in the main memory for execution. Most of the times there can be a requirement of many processes to be in the memory simultaneously for execution. This situation can prevent simultaneous execution of multiple processes due to the size of the main memory, which may not be large enough to hold all the processes. So, a concept of virtual memory was introduced.

A virtual memory management scheme allows execution of a process even if it is not completely in memory. That is, it requires only that

section of the process's code to be in the memory that will be executed. Generally, a process contains several functions or procedures and not all the functions are required to be in the memory at the same time. So the function or the procedure that will be executed needs to be in the main memory, while the other functions or procedures can be placed in the secondary memory and wait for their turn of execution. So whenever a function is not available in the main memory, it is brought from the secondary memory to main memory for execution. The main advantage of this scheme is that a program larger than main memory can still run on a smaller physical memory. This is how a games like *Need for speed* or *Call of Duty* which require respectively 30 GB and 90 GB of memory can still run on a system having 6 GB RAM with sufficient hard disk space. Also, as only a section of the code of a process needs to be in memory so many process can be there in memory simultaneously. Thereby increasing CPU utilization and throughput.

Figure 1.13 shows an example of a larger virtual memory than physical memory. The programmer thus need not have to worry about the size of the main memory available, thus can concentrate on the problem to be programmed. As can be seen in the Figure 1.13, pages from the large virtual memory address space is stored in the secondary memory and the pages are brought back to main memory whenever a call to those

pages are required. If the main memory does not have any free slot for the pages, then some page replacement algorithms are used to replace the pages in main memory with the pages from secondary memory.

Figure 1.14 shows dynamic memory allocation, where the stack grows upward and the heap grows downward. The gap shown in the figure between the heap and the stack is the part of virtual address space and will require physical memory space only if either heap or stack grows or both of them grows.

| 0   |       |

|-----|-------|

| 0   | code  |

|     | data  |

|     | heap  |

|     | Ļ     |

|     | 1     |

|     | stack |

| Max |       |

Figure 1.14: Virtual memory address space.

## **1.9.1 Demand Paging**

Suppose a user wants to run a program, so the entire program is loaded to main memory from the secondary memory. However, if the program runs one option/case out of the several cases based on the user input, it is impractical to load the code for all the cases, other cases my never be called for execution. So a virtual memory technique known as demand paging is used to load only those pages of the process when they are required or whenever there is a demand for the page occurs during the program execution.

Space for learners:

Figure 1.15: Example showing Demand Paging [1].

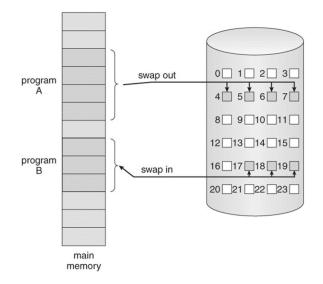

In Figure 1.15 shows and example of demand paging where pages 4, 5, 6 and 7 of Program A is swapped out of memory and pages 17, 18 and 19 of Program B is moved in to the memory because of the demand for the pages 17, 18 and 19. The method is implemented by a *pager* program responsible for demand paging.

## **1.10 PAGE REPLACEMENT ALGORITHMS**

Since operating system allows virtual memory to be larger than the main memory, as a result a page fault may occur. A page fault occurs when a running process tries to accesses a memory page that is not loaded in main memory. In the event of a page fault, the operating system may have to replace an existing page with the new page. A page replacement algorithm is required in an operating system that utilizes paging for memory management. It determines which page has to be replaced when a new page arrives. Different page replacement algorithms offer various methods for determining which pages to replace. All methods have the same goal: to decrease page faults.

## 1.10.1 FIFO Page Replacement

This is the most basic algorithm for replacing pages. The operating system uses this technique to maintain track of all memory pages in a queue, with the oldest page at the top. When a page has to be replaced, the first page in the queue is removed.

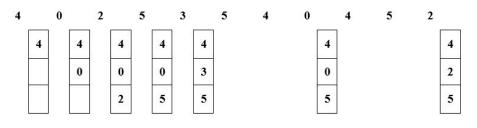

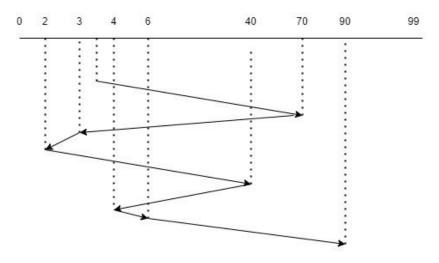

For example, consider the reference string 4, 0, 2, 5, 3, 5, 4, 0, 4, 5, 2 as shown in Figure 1.16 that is the order in which the memory references for the pages will be made. Assume that the memory which can accommodate three frames/pages at a time. The replacement algorithm uses the FIFO approach that is the first page moved to memory will be the first one to be replaced, this is followed by replacing second page, third page and so on with a new page. Initially, all the frames are empty so first three references (4, 0, 2) will result in page fault and are brought into the empty frames. The next reference 5 will replace the page 4 as it was the first page moved to the memory. Similarly, reference 3 will replace page 0 as it was the second page moved to memory. The next reference 5 is already in memory so no page fault and hence no page replacement. The process continues until all the page request in the reference string are processed. The total number of page faults using FIFO page replacement algorithm is 9.

| 4 |   | 0 |   | 2    |   | 5 |   | 3 |   | 5 | 4 | l. | 0 |   | 4 | 5 |   | 2 |   |  |

|---|---|---|---|------|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|--|

|   | 4 |   | 4 | 20 2 | 4 |   | 5 |   | 5 |   |   | 5  |   | 0 |   |   | 0 |   | 0 |  |

|   |   |   | 0 |      | 0 |   | 0 |   | 3 |   |   | 3  |   | 3 |   |   | 5 |   | 5 |  |

|   |   |   |   |      | 2 |   | 2 |   | 2 |   |   | 4  |   | 4 |   |   | 4 |   | 2 |  |

Figure 1.16: FIFO page replacement algorithm.

## 1.10.2 LRU Page Replacement

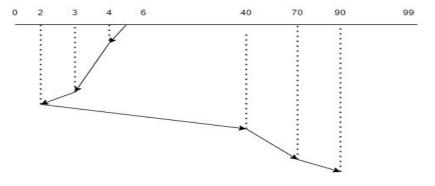

Least Recently Used (LRU) page replacement algorithm is a Greedy algorithm where the page to be replaced is the page which has not been used for the longest duration of time in the past. LRU keeps track of page usage over a period of time. It is based on the assumption that the

pages that have been extensively utilized in the past will also be heavily used in the future.

For example, consider the reference string 4, 0, 2, 5, 3, 5, 4, 0, 4, 5, 2 as shown in Figure 1.17 that is the order in which the memory references for the pages will be made. Assume that the memory which can accommodate three frames/pages at a time. Initially, all the frames are empty so first three references (4, 0, 2) will result in page faults and are brought into the empty frames. The next reference 5 will replace the page 4 as on scanning left starting at reference 5, we find that among the pages (4, 0, 2), page 4 is the least recently used page. Similarly, the next reference 3 will replace page 0 as on scanning left starting at reference 3, we find that among the pages (5, 0, 2), page 0 is the least recently used page. The next reference 5 is already in memory so no page fault and hence no page replacement. The process continues until all the page faults using LRU page replacement algorithm is 8.

| 4 |   | 0 | - | 2 | - | 5 | - | 3  |            | 5 | - | 4 |   | 0   |   | 4   | 5 | 2 |   |

|---|---|---|---|---|---|---|---|----|------------|---|---|---|---|-----|---|-----|---|---|---|

|   | 4 |   | 4 |   | 4 |   | 5 |    | 5          |   |   |   | 5 |     | 5 |     |   |   | 5 |

|   |   |   | 0 |   | 0 |   | 0 |    | 3          |   |   |   | 3 |     | 0 |     |   |   | 2 |

|   |   | 1 |   |   | 2 |   | 2 |    | 2          |   |   |   | 4 |     | 4 |     |   |   | 4 |

|   |   | 1 |   |   |   | 1 |   | TD | <u>т</u> т |   |   | 1 |   | × . | 1 | •.1 |   |   |   |

Figure 1.17: LRU page replacement algorithm.

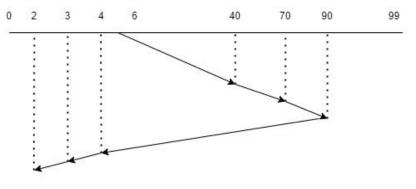

## 1.10.3 Optimal Page Replacement

The best page replacement algorithm is the Optimal Page Replacement algorithm, which produces the fewest page faults. This method replaces pages that will not be utilized for the longest period of time in the future. The algorithm is difficult to implement because it requires future knowledge of the pages referenced pages.

For example, consider the reference string 4, 0, 2, 5, 3, 5, 4, 0, 4, 5, 2 as shown in Figure 1.18 that is the order in which the memory references for the pages will be made. Assume that the memory which can accommodate three frames/pages at a time. Initially, all the frames are empty so first three references (4, 0, 2) will result in page faults and are brought into the empty frames. The next reference 5 will replace the

page 2 as on scanning right starting at reference 5, we find that among the pages (4, 0, 2), page 2 is not used for the longest duration of time. Similarly, the next reference 3 will replace page 0 as on scanning right starting at reference 3, we find that among the pages (4, 0, 5), page 0 is not used for the longest duration of time. The next reference 5 is already in memory so no page fault and hence no page replacement. The process continues until all the page request in the reference string are processed. The total number of page faults using LRU page replacement algorithm is 7.

Figure 1.18: Optimal page replacement algorithm.

|    | CHECK YOUR PROGRESS                                      | Space for learners |

|----|----------------------------------------------------------|--------------------|

| 1. | A memory buffer used to minimize the speed difference    |                    |

| b  | etween CPU and Main memory is called                     |                    |

|    | a) Main memory                                           |                    |

|    | b) Cache memory                                          |                    |

|    | c) register                                              |                    |

|    | d) disk buffer                                           |                    |

| 2. | Increasing the RAM improves performance because of       |                    |

|    | a) Increase in Virtual memory                            |                    |

|    | b) Bigger RAMs are faster                                |                    |

|    | c) Less page faults occur                                |                    |

|    | d) All of the above                                      |                    |

| 3. | Page fault occurs when                                   |                    |

|    | a) Exception is thrown                                   |                    |

|    | b) Requested page is not in memory                       |                    |

|    | c) Page is corrupted                                     |                    |

|    | d) Requested page is in memory                           |                    |

| 4. | Each logical address must be than the value in           |                    |

| 11 | mit register.                                            |                    |

|    | a) less than                                             |                    |

|    | b) equal to                                              |                    |

|    | c) Not equal to                                          |                    |

|    | d) greater than                                          |                    |

| 5. | Which one is the fastest memory                          |                    |

|    | a) Cache Memory                                          |                    |

|    | b) Associative Memory                                    |                    |

|    | c) Main Memory                                           |                    |

|    | d) Secondary memory                                      |                    |

| 6. | Fixed-sized blocks in physical memory is called          |                    |

|    | a) Block                                                 |                    |

|    | b) Frame                                                 |                    |

|    | c) Pages                                                 |                    |

|    | d) Segment                                               |                    |

|    |                                                          |                    |

| 7. | In paging CPU generated logical address has two partsand |                    |

| b)              | Page number & Page offset                                                                                                                                               | Space for learners: |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| c)              | Frame offset & displacement                                                                                                                                             |                     |

| d)              | Frame number & page offset                                                                                                                                              |                     |

| 8. Pa           | ging does not suffer from                                                                                                                                               |                     |

| a)              | Internal Fragmentation                                                                                                                                                  |                     |

| b)              | External Fragmentation                                                                                                                                                  |                     |

| c)              | Both a) and b)                                                                                                                                                          |                     |

| d)              | None of the above                                                                                                                                                       |                     |

| millis<br>ratio | it takes 10 milliseconds to search the TLB and 80<br>econds to access the physical memory. If the TLB hit<br>is 0.6, the effective memory access time (in<br>econds) is |                     |

| a)              | 120                                                                                                                                                                     |                     |

| b)              |                                                                                                                                                                         |                     |

| c)              |                                                                                                                                                                         |                     |

| d)              | 124                                                                                                                                                                     |                     |

| a)              | Greater than segment limit                                                                                                                                              |                     |

| b)              | Greater than the segment number                                                                                                                                         |                     |

| c)              | Between 0 and the segment number                                                                                                                                        |                     |

| d)              | Between 0 and segment limit                                                                                                                                             |                     |

| 11. In          | segmentation, each address is specified by                                                                                                                              |                     |

| a)              | A key and value                                                                                                                                                         |                     |

| b)              | A displacement and value                                                                                                                                                |                     |

| c)              | A segment number & displacement                                                                                                                                         |                     |

| d)              | A value and segment number                                                                                                                                              |                     |

| 12. Th          | e virtual memory manager loads only those component                                                                                                                     |                     |

| of or           | program during execution as a when required is known                                                                                                                    |                     |

| orap            | 1                                                                                                                                                                       |                     |

| as              |                                                                                                                                                                         |                     |

| as              | egmentation                                                                                                                                                             |                     |

- c) Virtual memory

- d) Demand Paging

## 1.11 SUMMING UP

- The five memory types in the hierarchy are register, cache, main memory, hard disk and magnetic tapes based on access time, speed, cost and capacity of the memory.

- Cache memory acts as a buffer between the main memory and the CPU.

- Associative memory is also known as Translation look aside Buffer (TLB) is a special type of memory that is optimized to perform parallel searches on data.

- Address protection is implemented with the help of two registers, the base register and the limit register.

- Paging is a memory management scheme that is used to map CPU generated logical address of a process to physical address in main memory.

- Logical Address is the address that is generated by the CPU for a running program.

- A physical address is the actual address in the main memory.

- Paging is a memory management scheme that is used to map CPU generated logical address of a process to physical address in main memory.

- The logical address generated by the CPU is divided into two parts namely page number and displacement with the page.

- Translation look aside Buffer is a small, expensive but very fast associative memory.

- In a translation look aside buffer, if the search page is found it is called as an TLB hit if the page is not found it called as TLB miss.

- The percentage of times that a particular page number is found in the TLB is called the hit ratio.

- Segmentation is a memory management scheme similar to paging that allows a process to be stored in the main memory in noncontiguous manner.

- The mapping of the logical address <segment-number, displacement> to the physical address is achieved with the help of segment table and the segmentation hardware.

- A virtual memory management scheme allows execution of a process even if it is not completely in memory.

- A virtual memory technique known as demand paging is used to load only those pages of the process when they are required or whenever there is a demand for the page occurs during the program execution.

- A page fault occurs when a running process tries to accesses a memory page that is not loaded in main memory.

- A page replacement algorithm is required in an operating system that utilizes paging for memory management. It determines which page has to be replaced when a new page arrives.

#### 1.12 ANSWERS TO CHECK YOUR PROGRESS

| 1. b | 2. c  | 3. b | 4. a | 5. b  |

|------|-------|------|------|-------|

| 6. b | 7. b  | 8. b | 9. b | 10. d |

| 11.c | 12. d |      |      |       |

#### **1.13 POSSIBLE QUESTIONS**

- 1. What is an associative memory? Why it is used?

- 2. How does the operating system ensure that two or more processes do not use the same address space?

- 3. Explain Paging memory management scheme.

- 4. What is hit ratio? Why page should be replaced in the memory?

- 5. Consider a logical address space of 16 pages of 512 words each, mapped on to a physical memory of 64 frames. How many bits are

there in the logical address? How many bits are there in the physical address?

- 6. If it takes 125 nanoseconds to search the TLB and 500 nanoseconds to access memory. If the hit ratio is 90%, calculate effective memory access time.

- 7. Assume a page size of 4K and an 18-bit logical address space. How many pages are in the system?

- 8. Assume that a CPU has a 16-bit logical address space with 4 logical pages. How large are the pages?

- 9. What is segmentation? Explain.

- 10. Define a virtual memory. With a neat diagram, explain the working of a virtual memory. What are the benefits of a virtual memory?

- 11. What is demand paging? Explain.

- 12. Consider logical address 1025 and the following

- 13. page table for some process P0. Assume a 15-bit address space with a page size of 1K. What is the physical address to which logical address 1025 will be mapped?

| 6 | 1 |

|---|---|

| 2 | l |

| 3 |   |

|   | ] |

|   | 1 |

14. Consider the following segment table:

| Segment | Base | Length |

|---------|------|--------|

| 34      | 100  | 100    |

| 21      | 2500 | 200    |

| 0       | 1200 | 50     |

| 90      | 1700 | 300    |

| 7       | 500  | 500    |

| 2       | 600  | 50     |

| 99      | 650  | 200    |

|         |      |        |

What are the physical address for the following logical address?

- i. 0,25 ii. 2,89 iii. 90,345 iv. 34,50

- v. 99,201

- 15. Consider the reference string 0, 3, 0, 4, 5, 3, 2, 0, 5, 4, 6, 7, 3, 4

Find the number of Page faults in each of the following cases assuming that memory can accommodate 4 pages/frames at a time.

- i. FIFO Page Replacement

- ii. LRU Page Replacement

- iii. Optimal Page Replacement

#### **1.14 REFERENCES & SUGGESTED READINGS**

- Operating System Principles 8<sup>th</sup> edition by Abraham Silberschatz, Greg Gagne, and Peter Baer Galvin, Willey

- Operating Systems: Internals and Design Principles 9<sup>th</sup> edition by William Stallings, Pearson Education

- Madnik and Donovan, Operating systems, McGraw Hill.

- Andrew, S. Tannenbaum, Modern operating system, PHI.

# **UNIT 2: INPUT-OUTPUT ORGANIZATION**

## Unit Structure:

- 2.1 Introduction

- 2.2 Unit Objectives

- 2.3 Input/Output peripherals

- 2.4 Accessing I/O devices

- 2.5 Polling

- 2.6 Interrupts

- 2.6.1 Handling multiple devices

- 2.6.2 Polling scheme

- 2.6.3 Vectored interrupt

- 2.6.4 Priority interrupt

- 2.6.5 Daisy chain

- 2.7 Direct memory access

- 2.7.1 Bus arbitration

- 2.8 Buses

- 2.9 Application I/O interface

- 2.10 Kernel I/O subsystem

- 2.10.1 I/O scheduling

- 2.10.2 Buffering

- 2.10.3 Caching

- 2.10.4 Spooling

- 2.10.5 Error handling

- 2.11 Summing Up

- 2.12 Answers to Check Your Progress

- 2.13 Possible Questions

- 2.14 References & Suggested Readings

# **2.1 INTRODUCTION**

Input and output peripherals are the key components of a computer system. The main task of a computer system can be categorized as Input/output and processing. In a computer system, the operating system (OS) is used to manage and control the input/output devices and perform operations on the data receives from I/O devices and output it. In this chapter, we will discuss the basic input/output hardware, Input/output services and interface provided by OS, how

# **2.2 UNIT OBJECTIVES**

After going through this unit, you will be able to:

- know about the I/O devices.

- understand different implementation issues related to I/O devices.

- explain how the I/O interface manages the gap between I/O devices and other units of a computer system.

- understand How to I/O devices are connected to a computer.

- learn about the I/O device controller.

- Learn how to access the I/O devices.

- explain how an OS handled interrupts and its different cases.

- understand how DMA is used to improve the throughput of a system.

- learn about the bus organization of a computer system.

- know about the functionalities of the kernel of an OS.

# 2.3 INPUT/OUTPUT PERIPHERALS

A computer system consists of four basic building blocks such as ALU, control unit, memory unit, and input/output unit. An input device can be defined as a hardware unit used to provide inputs into a system. The inputs may be a piece of data, information, control instruction, control signal, etc. The data or information can be of a different format – text, graphics, signals, etc., which is converted into a machine-understandable format by the input devices. The output hardware used in a computer system is keyboard, mouse, joystick, scanner, electronic pen, microphone, sensor devices, CCTV, light pen, trackball, graphic tablet, etc. The hardware peripherals used to get the output from the processor, project them or reproduce them in a human-understandable format can be defined as an output device/hardware. Output hardware's are monitor, printer, headphones, speaker, sound card, video card, plotter, screen

projector, speech synthesizer, GPS, etc. input/output hardware are may be wired or wireless.

To communicate with a machine, the I/O devices are connected with connection points of a machine known as a port. The I/O devices may use a common set of wires to transfer data/signals/addresses are known as a bus. A bus system in a computer can have three different types such as – to transfer data, data bus, control bus for transferring control signals, and address bus for transferring addresses in between processor and I/O devices or memory units.

A controller is used to control the I/O devices, system buses, and ports. A processor can send data and commands to the controller for performing I/O transfer. The controller has one or more registers to hold the data and commands. To read and write the device control registers the processor uses a set of standard data-transfer instructions and thus executes the I/O requests. The I/O device ports also have four registers namely – status, control, data in, and data out registers. The bits contained in the **status register** are used to depicting the states of completeness, availability of a byte of information to be read from the **data-in** register and occurring of a device, the bits in the control register are used. Reading the contents from the data-in register a host can access the inputs and by writing into the data-out register, a host can send output. The I/O device port registers are typically 1 - 4 bytes in size.

#### **STOP TO CONSIDER**

- 1. Certain bits in a control register of a serial port are used to choose a communication between full-duplex and half-duplex.

- 2. Other bits are used to check the parity.

- 3. Third bits are used to set the word-length between 7-8 bits.

- 4. Fourth bit is used choose the supported speed of the serial port.

# 2.4 ACCESSING I/O DEVICES

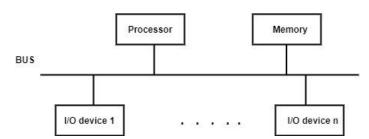

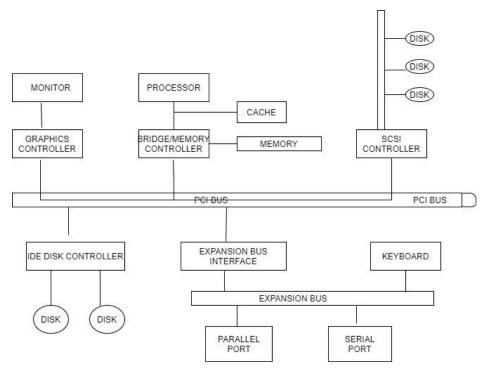

The computer system uses a common line to connect all the I/O devices with it called the bus. The bus system allows the I/O devices to exchange information as shown in **figure 2.1**. The bus system

199 | Page

typically consists of three different sets of lines: to transfer addresses – address

Figure 2.1: Bus structure of a computer system

bus, data – data bus, and control signals – control bus. Each I/O device has a unique set of specified addresses. When the processor placed a request by placing an address into the address line, any one of the connected devices will recognize it and respond to the command issued on the control line. During execution the processor request either a read or write command through the command line and transferred over the data bus. If the I/O device and the memory shared the same address space then the mechanism will be known as memory-mapped I/O.

The accessing speed of the I/O devices is varied from device to device and with the CPU also. The speed of the CPU is very high in comparison to the I/O devices. The CPU can execute millions of instructions when a user supplies input through an input device such as the keyboard. The CPU can execute the input character received from the keyboard, only after available in the input buffer of the keyboard interface.

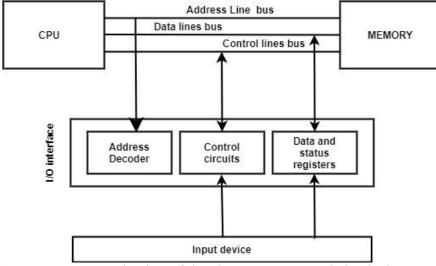

The I/O interface for each I/O device provides a platform to connect between the buses and the devices such that it can communicate data to and fro between the CPU and I/O devices. It has been depicted in figure 2.2. The interfaces are consists of four different set of registers – data in, data out, status and control registers.

Space for learners:

Figure 2.2: Communication of data between CPU and I/O devices

An input device interface for the keyboard sets the SIN bit of the status register as 1 if it has to perform an input operation. If the data is read by the processor for execution, it will be reset to 0. The SIN bit is regularly checked and read the data register. When the processor repeatedly checks for the status flag to get the required synchronization between the I/O device and the processor, is known as *program-controlled I/O*. Two other techniques to control the I/O device are interrupt-driven I/O and Direct memory access (DMA). Interrupt-driven I/O devices use to send an interrupt request over the bus to indicate that the device is ready for transferring data. In DMA, the I/O devices can directly communicate with the memory without intervening with the CPU frequently.

# 2.5 POLLING

The controller can announce its status using the **busy-bit** in the **status register**. The busy bit is set to 1 to state the status of the controller as busy and set to 0 when it is ready to accept the next command. The host machines announce the availability of commands to be executed by setting the **command-ready** bit. To place a command, a host repeatedly checks the busy bit until it becomes clear. The host sets the write bit into the command register and writes a byte into the data-out register. Then the host set the command bit ready. When the controller gets the command-ready as 1, immediately it sets the busy bit. The controller will read the command register and notice the write command. The controller

reads the data-out register to get the bytes of information and do the input/output to the device. After completion, the controller clears the command-ready bit, clears the error bit in the status register indicating the successful completion of the I/O operation, and clears the busy bit to indicate that the task is finished. When the host checks for the busyness of the controller by checking the status register repeatedly until the busy bit becomes clear or 0 is known as busy-waiting or polling. If the duration of a wait is long, the host may switch to another task. In many computer architectures, three CPU instruction cycles such as read a device register, logical-and to extract a status bit, and branch if not zero are sufficient to poll a device. Polling may be inefficient if the host repeatedly attempted for busy-bit but does not find any device ready for service due to the involvement of the CPU with incomplete processing. To overcome this problem, the hardware controller should inform the CPU, when the device becomes ready for service, rather than require the CPU to poll repeatedly for an I/O completion. The hardware mechanism that enables a device to notify the CPU is called an interrupt.

## **2.6 INTERRUPTS**

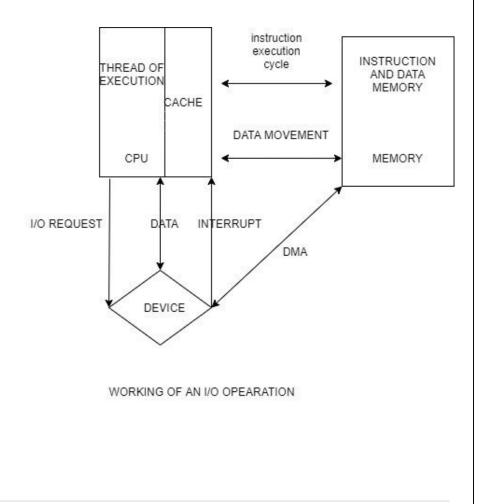

When an I/O device is busy performing a task for a long time, and the processor repeatedly asks for the status of the device, the processor may not execute any necessary computation within this time and seat idle. But the CPU can perform some other necessary computations while waiting for the I/O device to become ready. It is possible by sending a signal called an *interrupt* to the processor. Using the concept of interrupt the waiting cycle can be eliminated and increase the throughput of the system.

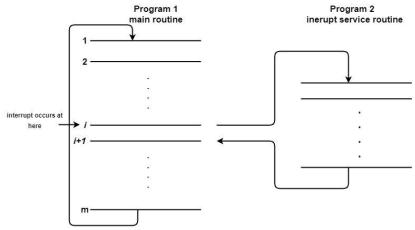

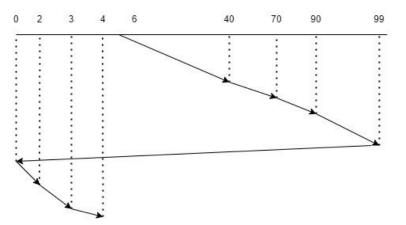

Interrupts is a hardware mechanism where the CPU senses the interrupt-request line after the execution of each instruction. Interrupts can take place at any time. The I/O device controller sets the interrupts-request line to get the CPU cycle at any time. If the CPU detects an interrupt in the interrupts request line, it immediately saves the current state on a processor stack and jumps to the interrupts handler routine. Suppose the CPU executing the  $i^{th}$  instruction during execution while the interrupt request arrives as shown in **figure 2.3**. The processor will complete the execution of the instruction *"i"* and load the program counter by the first instruction of the interrupt service routine. The address of the next

instruction i+1 will be stored onto the processor stack and after completion of the interrupt service routine, the PC will load the instruction i+1.

Figure 2.3: Execution of a program instruction by CPU

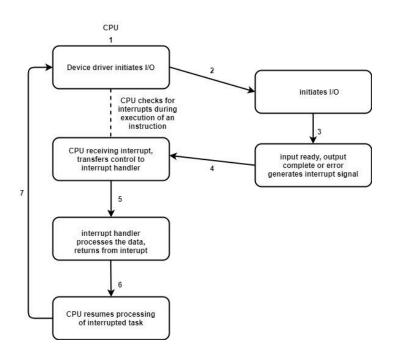

The interrupt handler routine determines the cause of the interrupt, performs the required operations, and executes the return-from operation to resume the CPU states before the interrupt. The following **figure 2.4** depicts a complete interrupts-driven input/output cycle. Input/output operations can be classified as synchronous and asynchronous.

Figure 2.4: Complete interrupt driven input/output cycle

In the case of a synchronous scheme, the CPU execution has to wait when the I/O devices are proceeds. But in the case of the asynchronous scheme, I/O operations can proceeds simultaneously with the CPU execution. The basic interrupt mechanism of a system allows the CPU to respond to an asynchronous event. To have an efficient input/output, the interrupt-controller hardware provides some more sophisticated features such as – ability to handle interrupt during complex processing tasks, the need to know about the interrupt initiating device without polling all the devices, and should support multilevel interrupt.

Two request lines – maskable and non-maskable are used by the CPU to identify the interrupt request type. In the case of a non-maskable interrupt, the CPU has to respond immediately by switching itself from its current execution. In case of a maskable interrupt, the CPU can turn off it such that the current execution is not interrupted.

## **2.6.1 Handling Multiple Devices**

A computer system may be connected with several I/O devices. There is no definite order in which I/O devices can request an interrupt, as the I/O devices are operationally independent. More than one device can activate the interrupt request line at the same time. This can raise some difficulties or issues in the system:

- i. How a processor can recognize the interrupt generating device.

- ii. If more than one device generates interrupt and maintain different interrupt service routine, then how the processor can recognize the starting address of the appropriate routine.

- iii. Is it necessary to allow another device to set the interrupt request line, while one device is already being served its interrupt service routine?

- iv. How to handle more than one interrupt generated exactly at the same time.

It is possible to handle more than one interrupt generated at the same time by breaking the tie and select any one of the two for service. After completion of the service routine of the selected device, the second one can be served. Some of the ways to handle multiple interrupts are:

#### 2.6.1.1 Polling Scheme

A device can indicate its interrupt request by placing 1 in one of the bits of the status register. The particular bit in the status register is known as IRQ. To identify the interrupt requested device, the interrupt service routine has to poll all the I/O devices connected with the bus system. For servicing, a dedicated subroutine will call a device, which encountered its IRQ bit set at first and is being served. It is easy to implement but wastes notable time during interrogating the IRQ bits of all the devices which are not requesting any service. To overcome this problem vectored interrupt mechanism has been used.

## 2.6.1.2 Vectored Interrupt

To reduce the time used in interrogating IRQ bits of each device in the polling scheme, vectored interrupt mechanism is used. Here the I/O device itself has to inform the CPU directly about its interrupt request. The interrupt requesting device sends the first address of its interrupt service routine to the processor over the bus as an indication of generating an interrupt. Then the processor can start the execution of the corresponding interrupt service routine from the specified starting address send by the device. This system enables the processor to recognize the interrupt request if any I/O device even activates a single interrupt request line. The location shared by the device with the processor has to be considered as the starting address of the interrupt service routine. The CPU loads the starting address onto the program counter which is known as the *interrupt vector*. Interrupt vector typically sends by the I/O devices over the data bus and the address length ranges in between 4 - 8 bits.

The processor may not respond to the interrupt vector immediately after requesting. The interrupts requesting devices have to wait to get the acknowledgment from the processor until the completion of the current execution. The interrupt requesting device can load its interrupt vector onto the bus if the CPU is ready to read it. While the processor is ready to read the interrupt vector, it enables the interrupt acknowledgment (INTA) line. The I/O device responds to the CPU by placing the interrupt vector onto the bus and turned off the INTR signal.

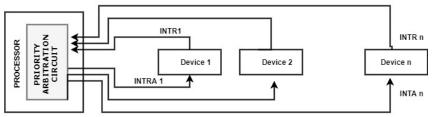

### 2.6.1.3 Priority Interrupt

When more than one device is involved in requesting an interrupt, the processor may have an arrangement to not allow other devices when one interrupt service routine is already is in process. Once an interrupt service routine is started to serve by the processor, it continues until completion of it and before the processor accepts an interrupt request from a second device. i.e. the second device has to wait until the completion of the current interrupt service routine execution. Sometimes the delay of execution may lead to an erroneous operation. Some of the waiting interrupt requests may have more priority than the executing one. To overcome this situation, the I/O devices have to arrange in a priority-based structure. Here the processor will accept the higher priority device request while servicing a device with lower priority.

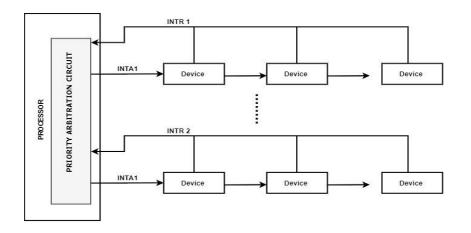

Figure 2.5: priority interrupt

If the processor accepts interrupt requests from other devices during the execution of an interrupt service routine; the accepting device will be selected based on device priority. This type of arrangement of I/O devices is known as a multiple-level priority organization. During the execution of a device request, the processor can accept interrupt requests from other devices which have a higher priority level than the current one. Once the processor has started to serve an interrupt service routine of a particular priority level, it disables interrupts from devices that have the same or lower priority level. The interrupt from higher priority devices may continue and be accepted. A multiple priority scheme can be implemented easily by using separate INTR and INTA lines for each device as shown in **figure 2.5**. In the diagram, each INTR line is assigned a different level of priority.

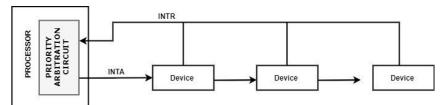

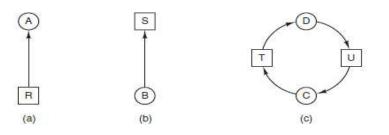

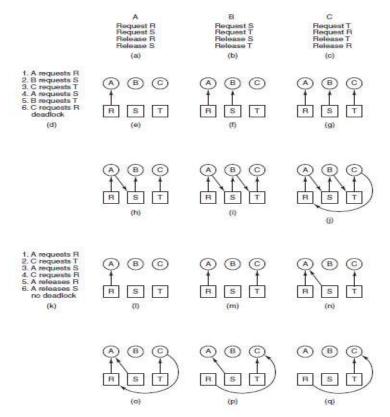

### 2.6.1.4 Daisy Chain

If more than one device generates interrupts simultaneously, in a multiple-level priority organization it is clear that the processor will serve the device with the highest priority. But in the case of vectored interrupt one device is select to send the interrupt request. Another efficient mechanism to solve this problem is the *daisy chain*. In this widely used scheme, all the I/O devices are shared a common interrupt request line for sending interrupt requests. But the processor uses only one interrupt acknowledgment (INTA) line to acknowledge the devices. The INTA line is connected in a daisy chain fashion, such as it passes through all the I/O devices as shown in figure 2.6. When the several I/O devices are activated the INTR line, the processor responds to it by enabling the INTA line. At first, the CPU serves device 1. If device 1 has a pending request, it will hold the INTA signal line until the operations have been completed. In the daisy chain arrangement, the device which is electronically closest to the processor has the highest priority. The second device along the chain has the second-highest priority and so on. In daisy chain arrangement the requirement of wires is less in comparison to the priority base structure as shown in figure 2.6.

Figure 2.6: Daisy chain

Figure 2.7: Daisy chain with priority based structure

Combining both the priority interrupt and daisy chain mechanism, a more general and useful interrupt handling mechanism can be achieved. An example of such a hybrid structure is depicted in the following diagram 2.7. Here the devices are combined to form a group of a particular priority level. Within the group, devices are connected in a daisy chain fashion.

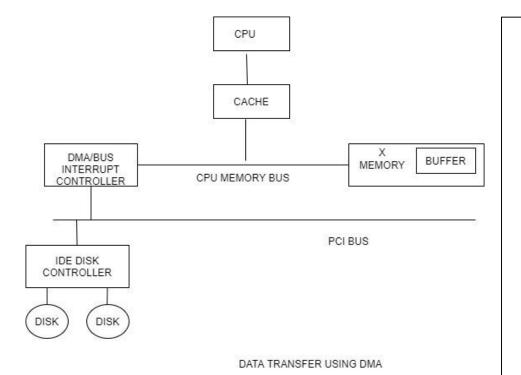

# 2.7 DIRECT MEMORY ACCESS

It has been observed from the previous sections that the I/O operations are mainly concentrated on the transfer of data between the processor and I/O devices. The processor can perform this by polling a device or the device itself can send an interrupt request to the processor. During this process involvement of the processor is very high. When the processor served an interrupt service routine, several program instructions have to be executed for each data word transfer. Additionally, the processor may be busy with polling the status register of each device, instruction to increment the memory address and keep a record of the word count. When an interrupt occurred, the additional overhead associated with the saving of currently executed instruction address into a stack, load the program counter by starting address of the interrupt service routine and again resume the previous execution. For transferring a large block of data directly in between the I/O device and the main memory, a different technique may use known as Direct Memory Access (DMA). In DMA the continuous intervention of the CPU is reduced by allowing the I/O devices to access the memory unit directly under the control of a special control unit. The control unit is a part of the device interface and performed the DMA transfer. This control circuit is known as the DMA controller. In general, the I/O devices are accessing the main memory through the processor. But in the case of DMA, the role of the processor is replaced by the DMA controller. The DMA controller is responsible for providing the required memory addresses and control signals needed for data transfer.

The controller unit performs the data transfer operation without interrupting the CPU, but the complete operation is under the control of the main program executed by the processor. To start an operation, the CPU sends the starting address, data words in the block, and the data flow direction to the controller. Once the DMA controller receives this information, it started to perform the

requested operation. After completion of the data transferring, the CPU is informed by the DMA through an interrupt signal and the processor removes the control from the DMA controller.

Space for learners:

# **STOP TO CONSIDER**

- 1. DMA transfers may have several attributes such as: Source address, destination address, transfer length, transfer type, block size, line stride, line length, etc.

- 2. DMA transfers can be categorized into two forms based on the hardware design and the involved peripheral devices, such as single cycle DMA and burst transfer.

During the data transfer using DMA, if the current execution cannot continue by the CPU, then CPU can switch the operation to some other which is ready in the ready queue. After receiving the interrupt signal from the DMA controller, the processor can return to the process requested for data transfer.

The entire operations of input/output are always performed by the operating system. OS is responsible for suspending a program executed by the processor and starting another one. Initiation of a DMA is also a task of the OS.

For example, to transfer a data block from the main memory to disk, a dedicated program writes the starting address and the word count of the data block into the corresponding registers of the disk controller. The DMA controller performs this operation independently without intervening in the CPU. After completion of the transfer of the data block, the done bit of the status and the control register are set. Simultaneously the controller sends an interrupt request to the CPU and sets the IRQ bit. The status register is used to store the information about proper transferring of the data block or if there occurred any error during data transfer.

The priority of demanding the bus system by DMA devices is always more than the processor. Among the DMA devices, the highest speed devices are getting higher priority than the others. Memory accesses by the processor and the DMA devices are interwoven. In a computer system, most of the memory access requests are generated by the processor itself. Thus it can be said that the DMA devices are stealing the memory cycles from the CPU. This mechanism is known as *cycle stealing*. It can be stated that the DMA devices are allowed to access the memory of a computer system exclusively to transfer a block of data without interruption and it can be defined as *block* or *burst* mode. But if the processor and the DMA controller or two DMA controllers request the main memory at the same time, then a conflict may arise. As a remedy or to resolve the conflict, a mechanism is used by the bus system to coordinate among the memory accessing devices is known as *bus arbitration*.

# 2.7.1 Bus Arbitration

A device known as a *bus-master* is used to control the initiation of the data transfer through the bus system at any time. When the bus master relinquishes control of the bus, another device may acquire it immediately. But using the bus arbitration mechanism, the next device which is going to be the bus master will be selected and the bus master ship will be transferred. There are two arbitration processes namely centralized and distributed arbitration. A single bus arbiter is used to perform the required arbitration in centralized arbitration. In the case of distributed bus arbitration, all the devices participating in the selection process of the next bus master.

# 2.8 BUSES

The prime units of a computer system are interconnected through a common bus system. The common bus is used to transfer data, addresses, and control signals among the prime computer units such as memory, processor, I/O devices, and the control unit. The line required in bus arbitration and interrupt are also included in this common bus system. During transferring information a set of rules have to be followed by the buses known as protocols. A bus protocol can be defined as a set of rules to govern the behaviour of interconnected devices. There are three kinds of buses available in a system. To transfer data – data bus, to transfer addresses – address bus, and to transfer control signals – control bus.

In the control lines, a single R/W signal is used to indicate, either read or write operation to be performed on memory. If the signal bit is set to 1 means a read operation, and 0 indicates a write operation. These lines are also used to carry time information, at what time a

device will perform the read/write operation i.e. at what time a device will place data onto the bus or at what time receives data from the bus. Based on the timing of data transfer over a bus, two different categories can be obtained – synchronous and asynchronous bus systems.

In an asynchronous bus system, all the devices derived the time from a common clock. Equal time duration is assigned for each device in the synchronous bus. Each of the time intervals of equal size is known as the bus cycle. One word of data can transfer in a bus cycle.

In an asynchronous bus system, the common clock is replaced by two-time control lines such as *Master-ready* and *Slave-ready*. This method is based on the use of a handshake between the master and slave. Here at first, the master indicates about the data whether it is ready for transmission or not, and second, the slave will respond to it. According to the handshaking protocol – the master will place the command information and addresses on the bus. It indicates the activation of the master-ready line and it is received by all the interconnected devices. At this point, all the devices have to decode their addresses. The slave line performs the required operation and informs the CPU by activating the slave-ready line. A full handshaking method can provide the highest degree of flexibility and reliability.

# **2.9 APPLICATION I/O INTERFACE**

I/O interfaces are used to enable the I/O devices and treat them in a standard and uniform manner. I/O interfaces can be customized with a layer known as the device drivers. Device drivers are used to hiding the differences between the device controllers from the I/O subsystem of the kernel. The use of the driver application encapsulates the behaviour of the devices in a few generic classes that hide the hardware differences from applications. It makes the operating system (OS) independent of the hardware and simplifies the job of the OS developers. This process restricts the device manufacturer either to manufacture a product that is compatible with the existing host controller interface of the OS or write a device driver to interface the new hardware to facilitate the OS. Thus a new device can be added to a computer through an OS. For different OS types, the device drivers may vary. For example, a graphics driver

for MS-DOS may not be supported by the OS, MS- Windows 2000, or in MAC OS.

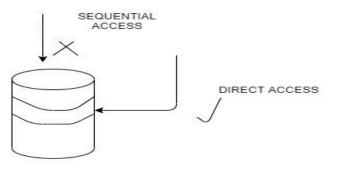

The devices can be categorized based on the data transfer style. The *character-stream* device transfers the data byte by byte whereas the *block device* transfers a block of bytes as a unit at a time. The keyboard is an example of a *character stream* interface. In a *sequential device* data transfer occurred in a fixed order determined by the device, whereas a *random access device* can instruct the device to search data on any available memory location randomly. Some of the devices perform data transfer within a predictable response time known as *synchronous devices*, whereas some of them show irregularity or in-predictable response time known as an *asynchronous device*. A *sharable device* can be accessed by several processes or threads but a *dedicated device* cannot. Some of the devices can perform both *read/write* operations, but some of them can perform either read or write operations i.e. transfer of data in only one direction.

### **STOP TO CONSIDER**

- 1. The device drivers are always operated within the kernel of an OS.

- 2. Kernel is the core part of an OS, which has direct access to the computer hardwares.

- 3. Device drivers are splitted into two layers such as logical and physical layer.

- 4. Broad classification catrgories of device drivers are: kernel device drivers and user mode device drivers.

The block device interface will collect all the related information for accessing disk drivers and other block-oriented devices. These devices are expecting commands like *read()* or *write()*. Random access devices can expect to have a *seek ()* command to locate the address of the next block to be transferred. To interact with the network devices, most of the OS including UNIX, Windows NT have used a network socket interface.

The computer system has *clock* and *timer* hardware to provide some basic functions such as current time, elapsed time, and a timer to perform trigger operations. The hardware used to maintain the trigger and the elapsed time is known as a *programmable interval*

*timer*. The OS provides an interface to the user to control the timer. During the power cut or shut-down mode of a system, a CMOS cell is used to supply power to the clock and timer.

# 2.10 KERNEL I/O SUB SYSTEM

The kernel of an OS provides lots of functionalities related to input/output such as – scheduling, caching, buffering, spooling, device reservation, error handling, etc. The kernel also protects the system from malicious software and errant processes.

# 2.10.1 I/O Scheduling

The kernel subsystem scheduled the I/O request such that the devices can perform their operations in an ordered manner. I/O scheduling can improve the system performance by fairly distributing the devices among the processes and thus improve the average waiting time. To implement I/O scheduling a wait queue containing I/O requests for the devices to be maintained. If an application is issued a blocking I/O system call, then the I/O request will be kept in the wait queue for that particular device. The I/O scheduler may rearrange the contents of the wait queue to improve the system performance and average access time experienced by the applications. In the case of an asynchronous I/O, the I/O scheduling has to keep track of many I/O requests simultaneously. The efficiency of a computer system can be improved by using other techniques that use storage in main memory or a disk via buffering, caching, and spooling.

### **STOP TO CONSIDER**

- 1. Different scheduling algorithms are used by an OS to scheduled the operations of I/O devices.

- 2. First Come First Serve (FCFS), Shortest Job First (SJF), Priority scheduling, Round robin etc. are the prime scheduling algorithms.

# 2.10.2 Buffering

Before transferring data from a device to another device or device to application, maybe store it in a memory area temporarily known as a buffer. Buffering is done due to three reasons. First, cope up with the speed mismatch between the speed of the producer and the consumer. The second, to provide adaptation for devices that have different data transfer sizes. A third use of buffering is to copy semantics for application I/O. Copying of data between kernel buffer and application data space is common in the operating system despite the overhead that this operation introduces, because of the clean semantics.

# 2.10.3 Caching

Cache memory is a faster memory placed in between the processor and the main memory. Caching is used to reduce the speed compatibility of the processor and the memory access time. It stores a block of data word into it which is being used by the processor shortly. The difference between buffering and caching is that in buffering an existing copy of data is hold whereas in cache a copy of data items can be store that can remain elsewhere.

# 2.10.4 Spooling

The output stream of data has to store in a buffer before going to an output device. It is known as spooling. A printer can be used to print the output of a process at a time, but many applications can request the printer at a time to print their output concurrently without mixing the outputs. The OS allows this by intercepting all the outputs to the printer. The output of each application is spooled into a separate disk file. Once the current printing process is being over, spooling system copied the next output to be print from the queue. It can copy one output from the queue to the printer at a time.

# 2.10.5 Error Handling

Using protected memory, an OS can protect a system from loss of data or information due to any errors that occurred in hardware or at the application level. Thus a system can protect from small mechanical faults. Devices and I/O data transfer may fail due to

several reasons. It may be either transient such as when a network becomes overloaded or for permanent reasons such as when a disk controller becomes defective. An OS can handle transient kinds of failures effectively.

### CHECK YOUR PROGRESS

### Choose the correct options for the following questions:

1. Which of the following is a major part of the time taken when accessing data on the disk?

- A. Settle time

- B. Rotational latency

- C. Seek time

- D. Waiting time

### 2. How does the hardware trigger an interrupt?

- A. Sending signals to CPU through the system bus

- B. Executing a special program called interrupt program

- **C**. Executing a special program called system program

- D. Executing a special operation called system call

- 3. Which operation is performed by an interrupt handler?

- A. Saving the current state of the system

- B. Loading the interrupt handling code and executing it

- C. Once done handling, bringing back the system to the original state it was before the interrupt occurred

- D. All of these

- 4. Which of the following is an example of the spooled device?

- A. A graphic display device

- B. A line printer used to print the output of several jobs

- C. A terminal used to enter input data to a running program

- D. A secondary storage device in a virtual memory system

5. An application loads 100 libraries at start-up. Loading each library requires exactly one disk access. The seek time of the disk to a random location is given as 10 ms. The rotational speed of the disk is 6000 rpm. If all 100 libraries are loaded from random locations on the disk, how long does it take to load all libraries? (The time to

transfer data from the disk block once the head has been positioned at the start of the block may be neglected)

> A. 0.50 s B. 1.50 s C. 1.25 s D. 1.00 s

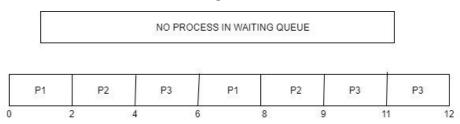

6. Consider the following table of arrival time and burst time for three processes P0, P1, and P2.

Process Arrival time Burst Time

| PO | 0 ms | 9 ms |

|----|------|------|

| P1 | 1 ms | 4 ms |

| P2 | 2 ms | 9 ms |

7. The pre-emptive shortest job first scheduling algorithm is used. Scheduling is carried out only at the arrival or completion of processes. What is the average waiting time for the three processes?

A. 5.0 msB. 4.33 msC. 6.33 msD. 7.33 ms

8. Let the time taken to switch between user and kernel modes of execution be t1 while the time taken to switch between two processes be t2. Which of the following is TRUE? (GATE CS 2011)

A. t1 > t2 B. t1 = t2 C. t1 < t2

D. Nothing can be said about the relation between t1 and t2

9. A set of wires and a rigidly defined protocol that specifies a set of messages that can be sent on the wires.

A. Port

B. Node

C. Bus

D. None of these

10. The \_\_\_\_\_\_ presents a uniform device-access interface to the I/O subsystem, much as system calls provide a standard interface between the application and the operating system.

- A. Devices

- B. Buses

- C. Device drivers

- D. I/O systems

- 11. The interrupt vector contains

- A. The interrupts

- B. the memory addresses of specialized interrupt handlers

- C. the identifiers of interrupts

- D. the device addresses

# 2.11 SUMMING UP

- An input device can be defined as a hardware unit used to provide inputs into a system.

- The hardware peripherals used to get the output from the processor, project them or reproduce them in a humanunderstandable format can be defined as an output device/hardware.

- To communicate with a machine, the I/O devices are connected with connection points of a machine known as a port.

- A controller is used to control the I/O devices, system buses, and ports.

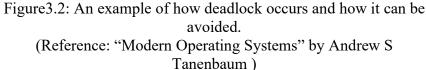

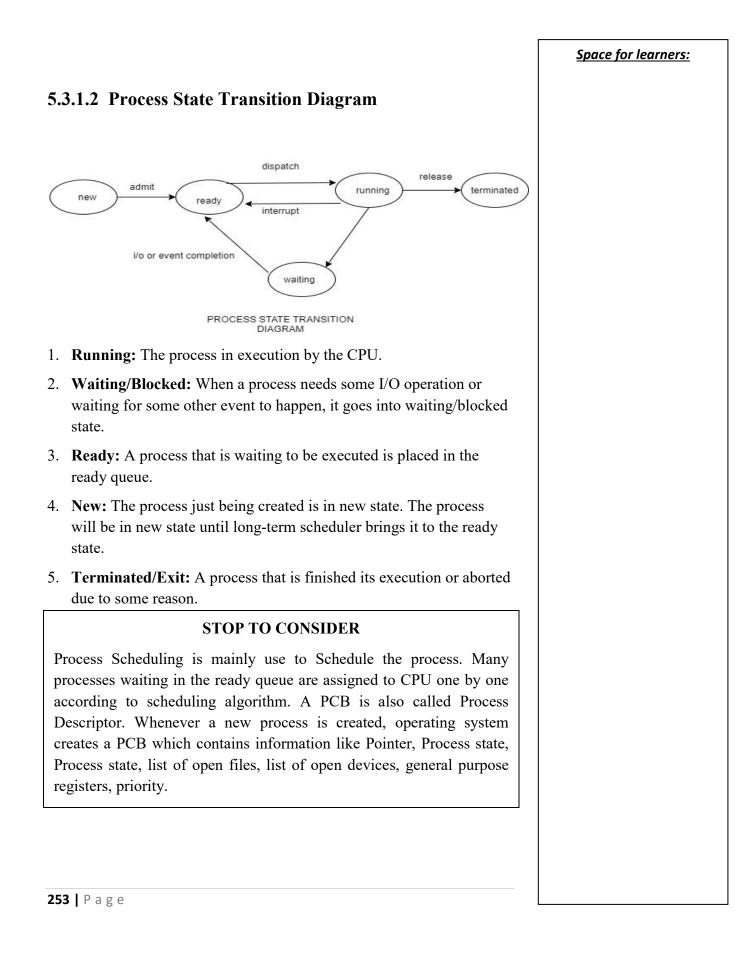

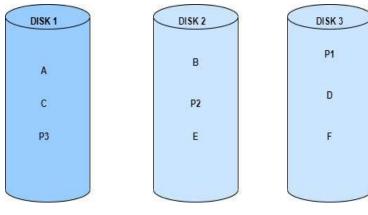

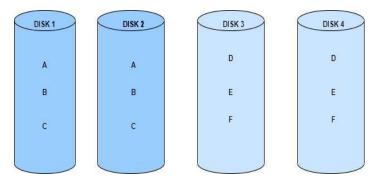

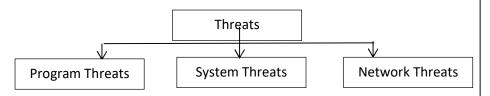

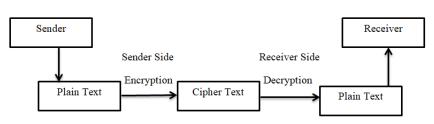

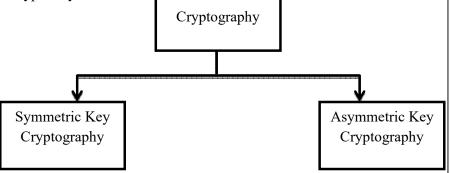

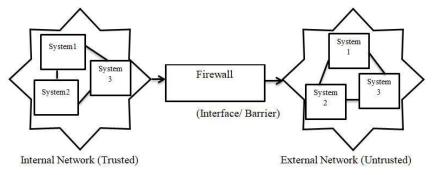

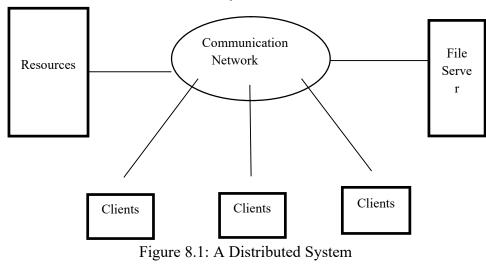

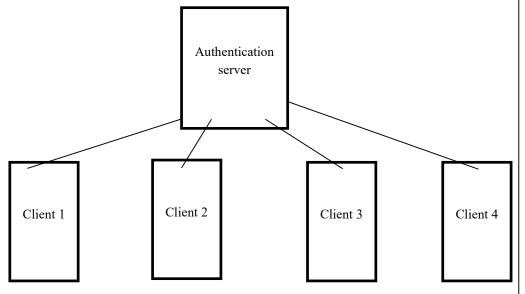

- The controller has one or more registers to hold the data and commands.